For (ii), the answer may be infinitely slow, i.e., no constraint on minimum. Input of the (leftmost) input register in cycle n where n = 0, 1, ….

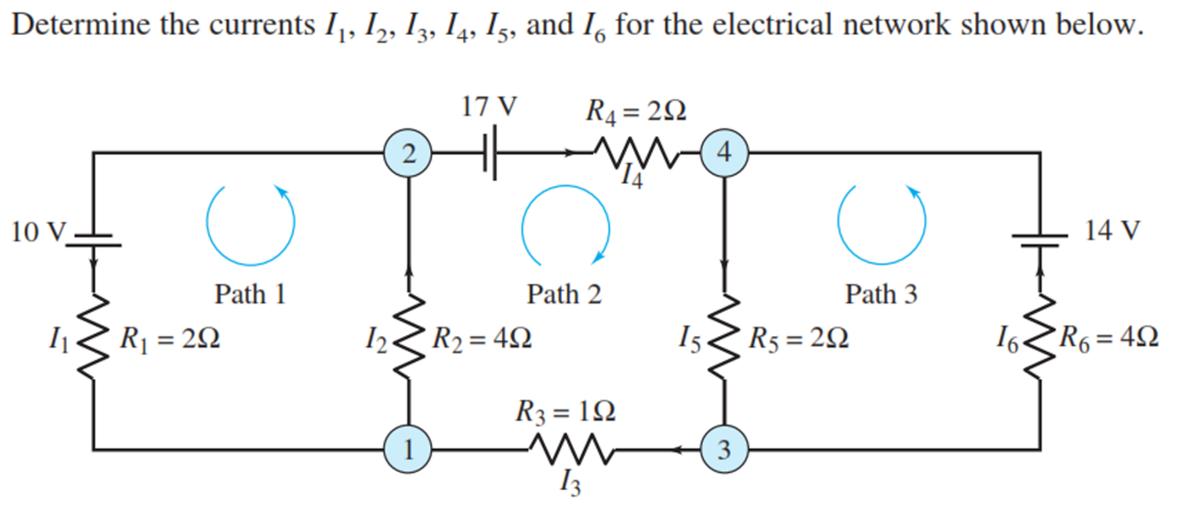

Finally, let the propagation and contamination delay of a multiplier be 5 t p d and 5 t c d A.2.1 For each of the circuit (both (a) and (b)) in Figure A.1, determine the following: Also, let the propagation and contamination delay of an adder/subtractor be t p d and t c d respectively. The register has a clockto-Q propagation delay t p c q and a clock-to-Q contamination delay of t cc q . Let the setup and hold time of each register to be t setup and t hold respectively. (a) original circuit (b) with 1 pipeline register (c) incorrectly pipelined circuit.

Figure A.1: Pipelining a feedforward circuit. The diagram also shows an incorrectly pipelined circuit that looks similar but produces wrong answers.

For instance, Figure A.1 shows several circuits with different pipelined datapaths that perform the same mathematical function: Y = A ( B − C ) + ( B − C ) ( A + B ) The diagram shows a correctly pipelined circuit that performs the same function except it has an additional pipeline stage and thus incurs an additional cycle of latency. A.2 Circuit Pipelining In theory, any feedforward circuits can be sped up by pipelining the datapath.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed